CN101123264A - 发光元件阵列和成像装置 - Google Patents

发光元件阵列和成像装置 Download PDFInfo

- Publication number

- CN101123264A CN101123264A CNA2007101408925A CN200710140892A CN101123264A CN 101123264 A CN101123264 A CN 101123264A CN A2007101408925 A CNA2007101408925 A CN A2007101408925A CN 200710140892 A CN200710140892 A CN 200710140892A CN 101123264 A CN101123264 A CN 101123264A

- Authority

- CN

- China

- Prior art keywords

- light

- emitting device

- emitting

- layer

- array

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission

- H01L27/153—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/435—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material

- B41J2/447—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material using arrays of radiation sources

- B41J2/45—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material using arrays of radiation sources using light-emitting diode [LED] or laser arrays

Landscapes

- Power Engineering (AREA)

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Optics & Photonics (AREA)

- Health & Medical Sciences (AREA)

- General Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Led Devices (AREA)

- Printers Or Recording Devices Using Electromagnetic And Radiation Means (AREA)

- Led Device Packages (AREA)

Abstract

发光元件阵列和成像装置。该发光元件阵列可以被制造而无需金属反射层的分离。该发光元件阵列包括提供在衬底上的多个发光元件部分,相邻发光元件部分之间的空间中至少一个空间彼此电分离,其中金属反射层提供在衬底上并且在多个发光元件部分下,并且用于发光元件部分之间的电分离的电阻层提供在多个发光元件部分与金属反射层之间。多个发光元件部分被划分成多个分块。每个分块包括多个发光部分。发光部分之间的电分离可以制造成作为相邻的不同分块中的相邻发光元件部分之间的电分离。

Description

技术领域

[0001]本发明涉及发光元件阵列和成像装置,特别地涉及具有高的光输出强度并且使用时分驱动操作的发光元件阵列,以及使用该发光元件阵列的成像装置。

背景技术

[0002]几千个发光二极管排列于其中的发光元件阵列用于电子照相印刷机的曝光光源。例如,通过在由GaAs等制成的化合物半导体衬底上形成每个包括几个AlGaAs层的元件结构,并且将它形成为阵列状态来生产阵列(日本专利第3185049号)。

[0003]当发光元件阵列用于印刷机时,根据期望的印刷分辨率确定元件大小和元件间隔是必要的。例如,在600dpi的情况下,减小元件大小到至少40μm的平方或更小并且减小元件间隔到大约40μm是必要的。在1200dpi的情况下,元件大小和元件间隔分别要求为一半。当发光元件阵列用作印刷机光源时,个别地驱动发光元件是必要的。实际上,时分驱动方法用作减少发光元件的电极的必要数目、驱动IC芯片的必要数目、以及丝焊的导线的必要数目的驱动方法,从而抑制成本的增加(日本专利3340626号)。

[0004]金属反射层提供在发光元件部分下面以提高提取效率,从而增加光输出强度(日本专利申请公开2005-197296号)。当光输出强度变高时,可以执行高速印刷。而且,光输出强度以小的电流值达到期望的强度,使得可以实现具有小的由发热引起的不利影响,例如较差的设备特性、较差的设备使用寿命或者较大的发光区域偏移的高清晰度印刷机光源。

[0005]到目前为止,当金属反射层提供在发光元件部分下面时,行进到衬底一侧的光可以在金属反射层上反射并且可以从元件表面提取,从而增加光输出强度。通常,金属层具有高导电性,使得使用通过积极地利用金属层的导电性在垂直方向上容易执行电流注入的方法。

[0006]当排列多个发光元件以产生阵列时,例如,考虑形成单个n侧电极作为公共电极并且形成与所有发光元件相对应的p侧电极以驱动发光元件的方法。这是通常称作静态驱动方法的基础驱动方法。但是,例如,当要在A4大小的情况下实现1200dpi的分辨率时,元件数目是一万或更多,并且元件密度变得非常高。因此,没有独立地放置p侧电极的空间,从而导致难以执行用于与驱动IC芯片的连接的丝焊的问题。

[0007]即使在大约600dpi的分辨率的情况下,需要5000或更多元件以实现A4大小从而需要5000或更多驱动IC芯片以及用于丝焊的5000或更多导线。因此,减少这些数目的方法对于成本减少是期望的。

[0008]为了解决上面的问题,使用时分驱动。这也称作动态驱动。根据该驱动,虽然发光元件以时分来驱动,但驱动所有元件所必需的电极的数目可以减少。在该情况下,电极布线是矩阵布线。在矩阵布线中,不提供单个公共电极,而是形成多个公共电极(例如n侧电极),假设为包括多个发光元件的每个分块形成每个公共电极。另一方面,为所有元件独立地布置具有另一种导电型的电极(例如p侧电极)不是必需的。当要提供的p侧电极的数目等于包括在形成有公共电极的分块中的所有元件的数目时,所有元件可以基础地驱动。在该情况下,p侧电极不仅与一个分块中的一个元件连接,而且与包括在不同于该一个分块的其他分块中的其他元件连接。也就是,多个元件通过使用一个p侧电极而驱动。

[0009]图11是说明时分驱动的说明图。发光元件(发光元件部分)L1-L9被划分成三个分块。第一分块包括三个发光元件L1-L3,第二分块包括三个发光元件L4-L6,以及第三分块包括三个发光元件L7-L9。n侧电极11-1,11-2和11-3为包括在各自分块中的发光元件而提供。p侧电极17-1,17-2和17-3为位于每个分块中的相同排列位置的发光元件而提供。在包括发光元件L1-L3的第一分块中,当n侧电极11-1由一个开关选择并且维持在接地(GND)电势时,由另一个开关从17-1至17-3中选择p侧电极中的一个以提供电流到光将从其中发出的目标发光元件。类似地,在包括发光元件L4-L6的第二分块中,当选择n侧电极11-2时,由另一个开关从17-1至17-3中选择p侧电极中的一个。类似地,在包括发光元件L7-L9的第三分块中,当选择n侧电极11-3时,由另一个开关从17-1至17-3中选择p侧电极中的一个。时分驱动由上述操作执行。

[0010]在下文,将描述用于静态驱动和时分驱动的、使用AlGaAs的发光元件阵列的结构实例。图12和13分别是说明能够执行静态驱动的发光元件阵列的横截面视图和平面图。在该实例中,提供总共九个发光元件(发光元件部分)。需要九个独立的p侧电极17和一个公共n侧电极11,也就是总共十个电极。在图12和13中,n型AlGaAs层13,AlGaAs量子阱活性层14,p型AlGaAs层15,p型GaAs接触层16和p侧电极17在n型GaAs衬底12上形成。为了元件分离,形成分离凹槽(元件分离凹槽)18以便到达n型AlGaAs层13。在区域21中,绝缘薄膜19在通过刻蚀而暴露的n型AlGaAs层13的一部分上形成,以便电绝缘。在区域22中,绝缘薄膜19的一部分在剩余而没有刻蚀的p型GaAs接触层16上形成。在发光区域23的每个中,p侧电极17的一部分与p型GaAs接触层16的顶面直接接触。当电流从p侧电极注入时,光从区域23发出。绝缘薄膜19提供在区域21和22中而不提供在区域23中,使得电流可以通过相应的p侧电极17仅注入到必要的发光区域23。提供分离凹槽18的每一个以使得相邻的发光元件彼此电分离。

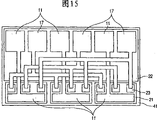

[0011]图14和15分别是说明能够执行时分驱动的发光元件阵列的横截面视图和平面图。与图12和13中说明的元件相同的构成元件由相同的参考数字表示。在图14和15中说明的1/3时分驱动中,如参考图11描述的那样使用3×3的矩阵布线,所有像素可以由三个公共n侧电极和三个公共p侧电极,也就是总共六个电极驱动。

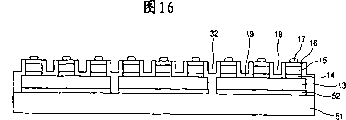

[0012]根据该方法,当增加时分的数目时,电极数目可以显著地减少。但是,不像静态驱动,形成多个公共电极是必要的。在正常情况下,使用半绝缘衬底31并且形成到达至少衬底31表面的分离凹槽32,使得可以相对容易地形成多个公共电极。提供分离凹槽32以使每个分块的发光元件彼此电绝缘。如上所述,在使用金属反射层的发光元件阵列的情况下,由于金属反射层而期望发光强度的增加。当每个分块的电绝缘对于时分驱动为必需时,金属反射层的导电性变成为此目的的问题。因此,如图16中说明的,形成不仅到达半导体层而且到达金属反射层52的分离凹槽是必要的。在仅半导体层的分离的情况下,刻蚀过程执行一次。但是,在金属反射层的分离的情况下,不同的刻蚀过程通常是进一步必要的,结果出现成本增加和产量减少的问题。

发明内容

[0013]已经作出本发明以解决上述问题。本发明的目的在于提供一种发光元件阵列,其光输出强度特别高并且可以低成本利用时分驱动来操作。

[0014]根据本发明,一种发光元件阵列包括:衬底;提供在衬底上的多个发光元件,相邻发光元件之间的空间中的至少一个空间电分离;提供在衬底上并且在多个发光元件下的金属反射层;以及提供在多个发光元件与金属反射层之间的电阻层,用于发光元件之间的空间的电分离。

[0015]此外,本发明提供一种阵列光源,包括:衬底;金属反射层;通过金属反射层提供在衬底上的多个发光元件;以及提供在金属反射层与发光元件之间以电分离金属反射层和发光元件的电阻层。

[0016]此外,本发明提供一种阵列光源,包括:衬底;公共金属反射层;每个包括多个发光元件的第一发光元件组和第二发光元件组,第一和第二发光元件组通过公共金属反射层提供在衬底上;提供在第一和第二发光元件组与金属反射层之间,用于金属反射层与第一和第二发光元件组之间的电分离的分离层;以及提供在第一发光元件组与第二发光元件组之间,用于第一发光元件组与第二发光元件组之间的电分离的分离凹槽,其中提供分离凹槽使得分离凹槽在从发光元件一侧朝向衬底一侧的方向上到达分离层。

[0017]根据本发明,电阻层提供在多个发光元件部分下和金属反射层上。因此,可以制造发光元件阵列而不分离金属反射层,从而阵列形成过程可以显著简化,并且可以减少制造成本。利用时分驱动来操作的阵列可以由简单的过程制造。这对于实现等于或大于600dpi的分辨率的阵列具有大的效果。

[0018]本发明的更多特征将从下面参考附图的示例性实施方案的描述中变得明白。

附图说明

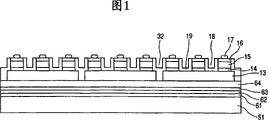

[0019]图1是说明根据本发明第一实施方案的发光元件阵列的横截面视图。

[0020]图2是说明根据本发明第一实施方案的发光元件阵列的平面图。

[0021]图3是说明本发明第一实施方案中生产元件阵列的步骤的说明性横截面视图。

[0022]图4是说明本发明第一实施方案中生产元件阵列的步骤的说明性横截面视图。

[0023]图5是说明根据本发明第二实施方案的发光元件阵列的横截面视图。

[0024]图6是说明本发明第二实施方案中生产元件阵列的步骤的说明性横截面视图。

[0025]图7是说明本发明第二实施方案中生产元件阵列的步骤的说明性横截面视图。

[0026]图8是说明根据本发明第二实施方案的发光元件阵列的平面图。

[0027]图9是说明包括根据本发明实施方案的发光元件阵列的电子照相记录过程型成像装置的结构图。

[0028]图10A和10B是活性层的电势图。

[0029]图11是说明时分驱动的图。

[0030]图12是说明能够执行静态驱动的一般发光元件阵列的横截面视图。

[0031]图13是说明能够执行静态驱动的一般发光元件阵列的平面图。

[0032]图14是说明能够执行时分驱动的一般发光元件阵列的横截面视图。

[0033]图15是说明能够执行时分的一般发光元件阵列的平面图。

[0034]图16是说明包括金属反射镜的常规发光元件阵列的横截面视图。

具体实施方式

[0035]在下文,将参考附图描述本发明的实施方案。

[0036](第一实施方案)

[0037]根据本发明第一实施方案的发光元件阵列包括提供在衬底与多个发光元件之间并且公共地用于多个发光元件的金属反射层。发光元件阵列还包括提供在多个发光元件与金属反射层之间的、用于发光元件之间的电分离的电阻层。根据该结构,元件可以彼此分离而无需在金属反射层自身中提供用于元件分离的凹槽。本发明不排除如果必要的话凹槽提供在金属反射层中的情况。

[0038]在下文,将参考图1等具体地描述本发明的第一实施方案。

[0039]图1是说明根据本发明第一实施方案的发光元件阵列的横截面视图。如图1中说明的,铂层61、金层62、银层63和无掺杂AlGaAs电阻层(用于电分离金属层与第一和第二发光元件组的层)64在Si衬底51上形成。n型AlGaAs层13、AlGaAs量子阱活性层14、p型AlGaAs层15、p型GaAs接触层16和p侧电极17进一步在无掺杂AlGaAs电阻层64上形成。提供绝缘薄膜19。为了元件分离,形成第一分离凹槽(元件分离凹槽)18以便到达n型AlGaAs层13。为了n侧公共电极分离,形成第二分离凹槽(n侧电极分离凹槽)32以便到达无掺杂AlGaAs电阻层64。第二分离凹槽32用于在n侧电极之间设置足够的电阻,从而将n侧电极彼此分离。第二分离凹槽到达至少无掺杂AlGaAs电阻层64。分离凹槽32可以到达用作金属反射层的银层63。提供每个分离凹槽18以使相邻的发光元件彼此电分离。提供分离凹槽32以电分离每个包括发光元件的分块。分离凹槽32的每个是电分离第一发光元件组(包括在一个分块中的多个发光元件)和第二发光元件组(包括在另一个分块中的多个发光元件)的分离凹槽。在图1中,为了简化,没有说明n侧电极(在图2中说明为n侧电极11)。

[0040]图1说明金属反射层包括从衬底51的一侧按次序排列的Pt层、Au层和Ag层的实例。但是,本发明并不局限于该实例。例如,单一的金属层(例如铝层或Ti层)和合金层中的一个可以用作金属反射层。TiN层或SiN层可以提供在用作反射层的金属层或合金层的顶面和底面上。例如,使用TiN/Al/TiN层的结构。

[0041]在图1中,与n型AlGaAs层相对应的部分可以由包括与活性层相邻的覆盖层和半导体多层反射镜(DBR镜)的结构代替。

[0042]有机绝缘薄膜(例如,正性光敏聚酰亚胺薄膜)可以置于无掺杂AlGaAs电阻层64与金属反射层(61,62,63)之间。

[0043]用于驱动发光元件的驱动IC电路置于其中的Si衬底可以用作Si衬底51。驱动IC电路包括位于Si衬底的绝缘区域中的晶体管。为了连接驱动IC电路和发光元件,如果必要的话,部分地去除金属反射层。

[0044]在该实施方案中,活性层具有量子阱结构并且其电势图在图10A中说明。在图10A中,n型AlGaAs层(覆盖层)13和p型AlGaAs层(覆盖层)15中的每一个的组成是例如Al0.4Ga0.6As(AlGaAs通常由AlxGa1-xAs(0<x<1)表示,其中x=0.4)。AlGaAs量子阱活性层14的组成例如是Al0.1Ga0.9As作为量子阱区域并且Al0.25Ga0.75As作为势垒区域。本发明的活性层的实例不仅包括上述量子阱活性层,而且包括具有单异质结构的活性层和具有双异质结构的活性层。

[0045]图2是说明根据上面实施方案的发光元件阵列的平面图。在该实施方案中,形成第一分离凹槽18使得元件大小和元件间隔中的每一个是20μm(在图2中L=20μm)。分块由第二分离凹槽32彼此分离,以便包括多个(在图2中为三个)发光元件。每个分块形成一个n侧电极11以便覆盖多个(在图2中为三个)发光元件。第一分离凹槽18到达N型AlGaAs层13。第二分离凹槽32到达至少无掺杂AlGaAs电阻层64。绝缘薄膜19沉积在第一分离凹槽18和第二分离凹槽32的每个中以进行电分离。电分离不一定通过分离凹槽的形成而实现。电分离可以通过例如绝缘区域的选择性形成而实现。电分离可以通过例如离子注入而实现。

[0046]多个(在图2中为三个)n侧电极11和多个(在图2中为三个)p侧电极17在绝缘薄膜19上以多层布线方式形成。n侧电极11的每个的仅必要部分与n型AlGaAs层13的相应一个直接接触。p侧电极17的每个的仅必要部分与p型GaAs接触层16的相应一个直接接触。电流可以通过n侧电极和p侧电极的适当组合的选择注入到期望的发光元件。剩余的n侧和p侧电极通过绝缘薄膜多层布线,使得电流注入区域不会不小心地扩展。另外,提供足够用于利用丝焊进行电连接的电极区。

[0047]如图2中说明的,在区域21的每个中,绝缘薄膜19在通过用于元件分离的刻蚀而暴露的n型AlGaAs层13的一部分上形成。在区域22中,绝缘薄膜19在剩余而没有刻蚀的p型GaAs接触层16上形成。在区域22中,虽然绝缘薄膜19在剩余的p型GaAs接触层16上形成,但替代地,刻蚀可以在形成分离凹槽32时执行,直到暴露无掺杂AlGaAs电阻层,然后绝缘薄膜19可以在其上形成。

[0048]在区域71中,绝缘薄膜19在通过用于n侧电极分离的刻蚀而暴露的无掺杂AlGaAs电阻层64上形成。在发光区域23的每个中,p侧电极17的一部分与p型GaAs接触层16的顶面直接接触。当电流从p侧电极的每个注入时,光从区域23中的相应的一个发出。绝缘薄膜19提供在区域21,22和71中而不提供在区域23中,使得电流可以通过相应的p侧电极71仅注入到必要的发光区域23。

[0049]接下来,将描述该实施方案中的元件阵列制造步骤。

[0050]如图3中说明的,具有与图1的层结构相反的层结构的元件构成层(相反元件构成层)通过外延生长在Si掺杂GaAs衬底12上形成。半绝缘GaAs衬底通常用于时分驱动。但是,半绝缘GaAs衬底具有高刻蚀坑密度。另外,当发光元件结构在半绝缘GaAs衬底上生长时,存在发光特性因其影响而劣化的情况。在该实施方案中,如随后描述的,提供在Si掺杂GaAs衬底12上的元件构成部分与Si掺杂GaAs衬底12分离并且转移到Si衬底。因此,可以使用衬底而不依赖于其导电性,并且通常可以使用具有低刻蚀坑密度的Si掺杂GaAs衬底12。

[0051]相反元件构成层通过在Si掺杂GaAs衬底12上按顺序形成AlAs选择性刻蚀分离层81、p型GaAs层16、p型AlGaAs层15、AlGaAs量子阱活性层14、n型AlGaAs层13和无掺杂AlGaAs电阻层64而形成。在该实施方案中,无掺杂AlGaAs电阻层64用作电阻层。因此,电阻层可以在元件构成层的外延生长期间形成。此外,最上表面是AlGaAs层,并且当为此使用高的Al组成时,存在AlGaAs层的表面氧化变成问题的情况。在该情况下,非常薄(大约5nm)的GaAs层可以作为盖层在最上表面上生长。

[0052]在外延生长之后,金属薄膜在晶片的表面和另外制备的用作支撑衬底的Si衬底的表面中的每一个上形成。具体地,银层63和金层62-1通过溅射法在Si掺杂GaAs衬底12上顺序形成,并且铂层61和金层62-2通过溅射法在Si衬底51上顺序形成。然后,金层62-1和62-2的表面彼此粘接。因为金材料具有高反射率并且金材料容易彼此粘接,所以金材料适合于在该实施方案中使用。但是,金材料与衬底的粘着新性通常较低。因此,为了提高粘着性,铂层61插入在不需要高反射率的Si衬底侧上,并且银层63插入在需要高反射率的GaAs衬底侧上。金层62-1和62-2彼此粘接以形成金层62。

[0053]随后,AlAs选择性刻蚀分离层81通过沉浸在氢氟酸溶液中而选择性地刻蚀,以分离GaAs衬底和元件构成层形成于其上的Si衬底。也就是,元件构成层(与相反元件构成层相反的层)从GaAs衬底转移到Si衬底(M.Konagai,M.Sugimoto和T.Takahashi,J.Cryst.Growth 45,277(1978))。从而,完成如图4中所示包括金属反射层的晶片。

[0054]随后,通过光刻技术对晶片构图并且分离凹槽通过湿法刻蚀或干法刻蚀在其中形成。如图2中说明的,元件大小和元件间隔中的每一个设置为20μm。刻蚀从表面执行并且当刻蚀到达n型AlGaAs层13时完成,从而形成第一分离凹槽18。然后,为了n侧接触形成再次执行构图并且n型AlGaAs层通过刻蚀而暴露。该步骤可以与第一分离凹槽的形成同时执行。进一步执行构图,并且第二分离凹槽32通过刻蚀而形成。至少分离凹槽32到达无掺杂AlGaAs电阻层64。分离凹槽32可以到达银层63。

[0055]此后,绝缘薄膜19沉积。通过在其上构图并刻蚀在绝缘薄膜中形成接触孔,使得n侧电极的接触部分和p侧电极的接触部分直接接合到元件的接触部分。然后,通过剥离执行的电极布线的形成和绝缘薄膜的沉积被重复几次以形成包括n侧电极11和p侧电极17的多层布线。最终,具有期望形状的芯片通过切割而获得,并且完成阵列芯片的生产。

[0056]为了通过时分驱动来驱动期望的元件,相邻n侧电极之间的电阻比p侧与n侧电极之间的电阻高。换句话说,当AlGaAs电阻层具有比p型AlGaAs层和n型AlGaAs层中的每个的电阻值高的电阻值时,可以防止电流流入包括在AlGaAs电阻层中的金属层中。AlGaAs电阻层的电阻值优选地是p型AlGaAs层和n型AlGaAs层中的每个的电阻值的十倍或更多的值。AlGaAs电阻层的电阻值更优地是p型AlGaAs层和n型AlGaAs层中的每个的电阻值的五十倍或更多的值。

[0057]无掺杂AlGaAs电阻层64的载流子密度是1×1016cm-3或更小。为了获得足够的电阻,在p型的情况下电阻层的载流子浓度,也就是其掺杂浓度期望是1×1017cm-3或更小。在n型的情况下,掺杂浓度期望是3×1016cm-3或更小。p型掺杂剂的实例包括C,Zn,Mg和Be,并且n型掺杂剂的实例包括Si,Ge,Te,Se和S。

[0058]电阻层的厚度是0.3μm。当电阻层太薄时,载流子从元件结构一侧扩散,使得流入金属薄膜中的无效电流增加。另一方面,当电阻层太厚时,这引起生产成本的增加或者光吸收的增加。因此,存在有效的厚度范围。期望的厚度设置为0.1μm至1μm。更期望的厚度设置为0.2μm至0.5μm。

[0059]为了充分获得光输出强度利用在金属薄膜上的反射而增加的效果,最小化由AlGaAs电阻层吸收的光量是重要的。因此,为了防止具有发光波长的光由AlGaAs电阻层吸收,调节AlGaAs电阻层的Al组成值是重要的。具体地,将AlGaAs电阻层的Al组分值设置为充分大于活性层的Al组分值的值是重要的。例如,当活性层的平均Al组分值是x%时,AlGaAs电阻层的期望Al组分值是(x+10)%或更多。在该实施方案中,活性层的平均Al组分值是17.5%,所以AlGaAs电阻层的期望Al组分值是27.5%或更多。

[0060]在该实施方案中,描述了活性层具有量子阱结构的情况。活性层可以是具有AlGaAs双异质结构的活性层。活性层具有AlGaAs双异质结构的情况的电势图在图10B中说明。用作活性层的AlGaAs层具有例如Al0.13Ga0.87As的组成,并且覆盖层具有例如Al0.4Ga0.6As的组成。在该情况下,活性层具有Al0.13Ga0.87As的组成从而Al组分值是13%,所以AlGaAs电阻层的期望Al组分值是23%或更多。

[0061]除了位于GaAs衬底上的发光元件构成层通过一次接合步骤提供在Si衬底上的情况之外,发光元件构成层可以临时转移到另一个支撑衬底然后转移到该Si衬底上。在该情况下,相反元件构成层不一定在GaAs衬底上形成。当发光元件构成层将最终转移到Si衬底上时,有机绝缘薄膜可以置于其间。在该情况下,金属反射层(不一定形成为多层薄膜)提前在Si衬底侧或发光元件侧上形成。

[0062](第二实施方案)

[0063]图5是说明根据本发明第二实施方案的发光元件阵列的横截面视图。本实施方案不同于图1的情况在于,SiO2薄膜101代替无掺杂AlGaAs电阻层位于金属反射层(银层63)上。SiO2薄膜用作电阻层,使得可以形成更高绝缘性的分离。其他构成元件与图1的那些相同。

[0064]将描述该实施方案中的元件阵列生产步骤。如图6中说明的,具有与图5的层结构相反的层结构的元件构成层通过外延生长在GaAs衬底12上形成。此时,AlAs选择性刻蚀分离层81刚好位于相反元件构成层下面。在随后进行选择性刻蚀之后,使用AlAs选择性刻蚀分离层81,以分离GaAs衬底12和相反元件构成层。在相反元件构成层(p型GaAs接触层16、p型AlGaAs层15、AlGaAs量子阱活性层14和n型AlGaAs层13)的外延生长之后,SiO2薄膜101以0.3μm的厚度沉积在生长表面上以形成电阻层。

[0065]此后,金属薄膜在晶片的表面和另外制备的Si衬底的表面中的每个上形成。与第一实施方案的情况一样,银层63和金层62-1通过溅射法在GaAs衬底12一侧上顺序形成,并且铂层61和金层62-2通过溅射法在Si衬底51一侧上顺序形成。然后,金层62-1和62-2的表面彼此粘接。然后,通过沉浸在氢氟酸溶液中仅选择性刻蚀AlAs选择性刻蚀分离层81以将元件构成层(与相反元件构成层相反的层)转移到Si衬底上。因此,产生如图7中说明的包括金属薄膜和SiO2薄膜的晶片。

[0066]随后,通过光刻技术对晶片构图并且分离凹槽通过湿法刻蚀或干法刻蚀在其中形成。如图8中说明的,元件大小和元件间隔中的每个设置为20μm。刻蚀从表面执行并且当刻蚀到达n型AlGaAs层13时完成,从而形成第一分离凹槽18。然后,为了n侧接触形成而再次执行构图,并且n型AlGaAs层通过刻蚀而暴露。该步骤可以与如上所述第一分离凹槽的形成同时执行。进一步执行构图,并且第二分离凹槽32通过刻蚀而形成。至少分离凹槽到达SiO2薄膜101。分离凹槽可以到达银层63。

[0067]此后,绝缘薄膜19沉积。通过绝缘薄膜的构图和刻蚀在绝缘薄膜中形成接触孔,使得n侧电极的接触部分和p侧电极的接触部分直接接合到元件的接触部分。然后,通过剥离执行的电极布线的形成和绝缘薄膜的沉积被重复几次以形成n侧电极和p侧电极的多层布线。最终,具有期望形状的芯片被切割,并且完成阵列芯片的生产。

[0068]为了通过时分驱动来驱动期望的元件,使相邻n侧电极之间的电阻充分高于p侧与n侧电极之间的电阻。换句话说,当电阻层具有比p型AlGaAs层和n型AlGaAs层中的每个的电阻值高的电阻值时,可以充分防止电流流入包括在其中的金属层。在该实施方案中,通常用作绝缘体的SiO2薄膜用作电阻薄膜,从而具有足够高的电阻值。除了SiO2之外,例如可以使用材料例如SiN、SiON、AlN或Al2O3。

[0069]SiO2薄膜的薄膜厚度是0.2μm。当SiO2薄膜太薄时,可能从元件结构一侧泄漏电流。另一方面,当SiO2薄膜太厚时,这会引起生产成本的增加或者光吸收的增加。因此,存在有效的厚度范围。期望厚度设置为0.05μm至0.5μm。更期望的厚度设置为0.1μm至0.3μm。

[0070]如上所述根据第一实施方案和第二实施方案的发光元件阵列在元件间隔较小的情况下特别有效。当元件间隔是40μm或更小时,也就是当分辨率是600dpi或更小时,本发明可以适用。

[0071]即使当根据第一实施方案和第二实施方案的发光元件阵列中的导电型改变成相反的导电型,也就是,即使当n型变成p型或者即使当p型变成n型时,本发明可以适用。

[0072]根据本发明的发光元件阵列的材料并不局限于实施方案中描述的AlGaAs材料。换句话说,可以使用用于其他发光器件的材料,例如基于AlGaInP的材料或基于AlGaInN的材料。即使当使用这些材料时,仍然获得足够的效果。

[0073]根据本发明的发光元件阵列的活性层并不局限于实施方案中描述的量子阱活性层,因此可以是例如具有AlGaAs双异质结构的活性层。当使用量子阱活性层时,可以提高发光效率。

[0074]接下来,将描述根据本发明的发光元件阵列的应用实例。根据本发明的发光元件阵列可以用作电子照相记录系统型成像装置的曝光光源。发光元件阵列可以用作用于其他应用的阵列光源。

[0075]图9是说明包括根据一种实施方案的发光元件阵列的电子照相记录系统型成像装置的结构图。

[0076]在图9中,成像装置包括:发光元件阵列半导体芯片安装于其上的曝光部分701,用作对置的光接收部分的光敏鼓702,鼓充电器703,用于调色剂沉积的显影设备704,用于将光敏鼓上的调色剂转印到位于传送带707上的纸张708上的转印设备705,以及用于在转印之后去除光敏鼓702上的剩余调色剂的清洁器706。

[0077]接下来,将描述曝光部分701。曝光部分701包括:发光元件阵列半导体芯片(单元片)710,发光元件阵列710的多个单元片位于其上的陶瓷基底711,以及用作光学系统的参考框架的铝制框架712。发光元件阵列半导体芯片710可以提供在圆柱形光敏鼓的内部。

[0078]曝光部分701还包括:焦点位于发光元件阵列半导体芯片710的发光点序列和光敏鼓702上的SELFOC透镜阵列,这是产品名(在下文仅称作“SLA”);以及产生防止调色剂分散的电场的电极714。曝光部分701还包括用于覆盖/支撑铝制框架712的相对一侧的模件715。电源716用来在电极714之间施加直流电压。开关717用来控制所施加的直流电压。

[0079]接下来,将描述纸张708上图像形成的流程。光敏鼓702由鼓充电器703均匀地负性充电。

[0080]然后,光敏鼓702由曝光部分701与图像图案相对应地曝光以对曝光部分正性充电,从而形成静电潜像。负性充电的调色剂从显影设备704供给到静电潜像以将调色剂吸引到正性充电的部分,从而在光敏鼓702上形成调色剂图像。

[0081]然后,调色剂图像通过转印设备705转印到纸张708上,以在纸张708上形成调色剂图像。

[0082]在转印之后,光敏鼓702上的剩余调色剂由清洁器706去除,然后操作再次返回到充电过程。

[0083]本发明用于发光元件阵列以及使用发光元件阵列的装置,例如包括发光元件阵列的电子照相记录系统型成像装置。

[0084]虽然本发明已经参考实例实施方案而描述,但是应当理解,本发明并不局限于公开的实例实施方案。下面权利要求的范围与最广泛的解释一致,以便包括所有这些修改以及等价结构和功能。

Claims (22)

1.一种发光元件阵列,包括:

衬底;

提供在衬底上的多个发光元件,相邻发光元件之间的空间中的至少一个空间电分离;

提供在衬底与多个发光元件之间、为多个发光元件共用的金属反射层;以及

提供在多个发光元件与金属反射层之间的电阻层,用于发光元件之间的空间的电分离。

2.根据权利要求1的发光元件阵列,其中形成包括发光元件的多个分块,以及

其中发光元件之间的空间的电分离是分别包括在不同分块中的相邻发光元件之间的空间的电分离。

3.根据权利要求1的发光元件阵列,还包括提供在彼此电分离的相邻发光元件之间的空间中的分离凹槽,

其中分离凹槽至少到达电阻层。

4.根据权利要求1的发光元件阵列,其中电阻层具有如下设置的电阻值:使得彼此电分离的发光元件之间的空间的电阻值大于包括在发光元件中并与电阻层接触的区域的电阻值。

5.根据权利要求1的发光元件阵列,其中电阻层由半导体制成。

6.根据权利要求1的发光元件阵列,其中电阻层由AlGaAs制成。

7.根据权利要求5的发光元件阵列,其中电阻层是无掺杂层。

8.根据权利要求5的发光元件阵列,其中电阻层是p型并且具有1×1017cm-3或更小的p型杂质的掺杂浓度。

9.根据权利要求5的发光元件阵列,其中电阻层是n型并且具有3×1016cm-3或更小的n型杂质的掺杂浓度。

10.根据权利要求1的发光元件阵列,其中电阻层具有至少大于等于0.1μm且小于等于1μm的厚度。

11.根据权利要求1的发光元件阵列,其中电阻层由绝缘体制成。

12.根据权利要求1的发光元件阵列,其中电阻层由选自SiO2,SiN,SiON,AlN和Al2O3的一种制成。

13.根据权利要求11的发光元件阵列,其中电阻层具有大于等于0.05μm且小于等于0.5μm的厚度。

14.根据权利要求1的发光元件阵列,其中发光元件利用时分驱动来操作。

15.根据权利要求1的发光元件阵列,其中发光元件具有40μm或更小间隔的发光区域。

16.一种成像装置,包括:

用于读取图像的图像读取单元;

根据权利要求1的发光元件阵列,用于基于由图像读取单元读取的图像而发光;以及

基于由发光元件阵列发射的光而形成图像的成像单元。

17.一种阵列光源,包括:

衬底;

金属反射层;

通过金属反射层提供在衬底上的多个发光元件;以及

提供在金属反射层与发光元件之间以电分离金属层和发光元件的电阻层。

18.一种阵列光源,包括:

衬底;

公共金属反射层;

第一发光元件组和第二发光元件组,每一个包括多个发光元件,第一和第二发光元件组通过公共金属反射层提供在衬底上;

提供在第一和第二发光元件组与金属反射层之间,用于金属层与第一和第二发光元件组之间的电分离的分离层;以及

提供在第一发光元件组与第二发光元件组之间,用于第一发光元件组与第二发光元件组之间的电分离的分离凹槽,

其中提供分离凹槽使得分离凹槽在从发光元件侧朝向衬底侧的方向上到达用于电分离的分离层。

19.根据权利要求18的阵列光源,其中衬底是硅衬底;并且阵列光源的发光元件的发光通过时分驱动来控制。

20.根据权利要求18的阵列光源,其中衬底还包括执行时分驱动的控制电路。

21.一种成像装置,包括:

根据权利要求17的阵列光源;

使用阵列光源作为曝光部分来形成静电潜像的光敏鼓;以及

使在光敏鼓上形成的静电潜像显影的显影设备。

22.根据权利要求21的成像装置,其中阵列光源提供在圆柱形的光敏鼓的内部。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006219791 | 2006-08-11 | ||

| JP2006219791A JP4960665B2 (ja) | 2006-08-11 | 2006-08-11 | 発光素子アレイ及び画像形成装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101123264A true CN101123264A (zh) | 2008-02-13 |

Family

ID=38616352

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2007101408925A Pending CN101123264A (zh) | 2006-08-11 | 2007-08-10 | 发光元件阵列和成像装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7786495B2 (zh) |

| EP (1) | EP1887627A3 (zh) |

| JP (1) | JP4960665B2 (zh) |

| KR (1) | KR100954051B1 (zh) |

| CN (1) | CN101123264A (zh) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105900239A (zh) * | 2013-09-30 | 2016-08-24 | 艾利迪公司 | 包括发光二极管的光电子装置 |

| WO2022094967A1 (zh) * | 2020-11-06 | 2022-05-12 | 京东方科技集团股份有限公司 | 发光二极管芯片及其制备方法、显示装置 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101571577B1 (ko) | 2008-02-29 | 2015-11-24 | 오스람 옵토 세미컨덕터스 게엠베하 | 모놀리식 광전자 반도체 본체 및 그 제조 방법 |

| DE102008011848A1 (de) | 2008-02-29 | 2009-09-03 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterkörper und Verfahren zur Herstellung eines solchen |

| EP2332185A2 (en) * | 2008-09-08 | 2011-06-15 | 3M Innovative Properties Company | Electrically pixelated luminescent device |

| EP2356701A2 (en) | 2008-11-13 | 2011-08-17 | 3M Innovative Properties Company | Electrically pixelated luminescent device incorporating optical elements |

| KR101055003B1 (ko) | 2010-03-09 | 2011-08-05 | 엘지이노텍 주식회사 | 발광 소자, 발광 소자 패키지, 조명 시스템, 및 발광 소자 제조방법 |

| CN103639314A (zh) * | 2013-11-15 | 2014-03-19 | 四川银河钢结构工程有限公司 | 钢卷送料机构 |

| DE102014101896A1 (de) * | 2014-02-14 | 2015-08-20 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optoelektronischen Halbleiterbauteils sowie optoelektronisches Halbleiterbauteil |

| US9502625B2 (en) | 2014-06-06 | 2016-11-22 | Rohinni, LLC | Electrophotographic deposition of unpackaged semiconductor device |

| KR102480220B1 (ko) | 2016-04-08 | 2022-12-26 | 삼성전자주식회사 | 발광 다이오드 모듈 및 이를 구비한 디스플레이 패널 |

| CN105817548B (zh) * | 2016-05-31 | 2017-11-21 | 蒙城县弘文信息科技有限公司 | 一种钢片输送冲压机构 |

| US10566507B2 (en) | 2017-01-12 | 2020-02-18 | Rohinini, LLC | Apparatus for high speed printing of semiconductor devices |

| KR102381562B1 (ko) * | 2017-03-10 | 2022-04-04 | 주식회사 루멘스 | 마이크로 엘이디 모듈 및 그 제조방법 |

| JP7305970B2 (ja) | 2019-01-28 | 2023-07-11 | 市光工業株式会社 | 車両用前照灯 |

| US20210151649A1 (en) * | 2019-11-18 | 2021-05-20 | Facebook Technologies, Llc | Bonding of light emitting diode arrays |

| FR3103634B1 (fr) * | 2019-11-21 | 2021-12-03 | Commissariat Energie Atomique | Procede de formation d’une electrode commune d’une pluralite de dispositifs optoelectroniques |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69024856T2 (de) | 1989-06-16 | 1996-06-05 | Canon Kk | Aufzeichnungsbogen für Bildaufzeichnungsgeräte sowie Verfahren und Apparat zur Bildherstellung |

| DE69023283T2 (de) | 1989-06-16 | 1996-04-18 | Canon Kk | Ausgabeblatt für Bilderzeugungsvorrichtung und Bilderzeugungsvorrichtung mit Nutzung des Blattes. |

| JPH07114311A (ja) | 1993-10-15 | 1995-05-02 | Fujitsu Ltd | 画像形成装置 |

| JP3340626B2 (ja) * | 1996-07-25 | 2002-11-05 | 沖電気工業株式会社 | 発光ダイオードアレイ及びその製造方法 |

| JP3185049B2 (ja) | 1996-11-12 | 2001-07-09 | 沖電気工業株式会社 | 発光素子アレイ及びその製造方法 |

| US5955747A (en) | 1996-07-25 | 1999-09-21 | Oki Electric Industry Co., Ltd. | High-density light-emitting-diode array utilizing a plurality of isolation channels |

| US6504180B1 (en) * | 1998-07-28 | 2003-01-07 | Imec Vzw And Vrije Universiteit | Method of manufacturing surface textured high-efficiency radiating devices and devices obtained therefrom |

| JP2001088345A (ja) | 1999-09-20 | 2001-04-03 | Sanyo Electric Co Ltd | 光プリントヘッド |

| JP2001307506A (ja) * | 2000-04-17 | 2001-11-02 | Hitachi Ltd | 白色発光装置および照明器具 |

| US7287678B2 (en) | 2001-11-16 | 2007-10-30 | Vamco International Inc. | Method and apparatus for determining and setting material release mechanism timing for a material feed mechanism |

| JP3824497B2 (ja) | 2001-04-18 | 2006-09-20 | 株式会社沖データ | 発光素子アレイ |

| JP2004207325A (ja) | 2002-12-24 | 2004-07-22 | Oki Data Corp | 半導体装置 |

| JP2005197296A (ja) | 2003-12-26 | 2005-07-21 | Shin Etsu Handotai Co Ltd | 発光素子及びその製造方法 |

| JP2005277372A (ja) * | 2004-02-25 | 2005-10-06 | Sanken Electric Co Ltd | 半導体発光素子及びその製造方法 |

| JP4799975B2 (ja) | 2005-09-16 | 2011-10-26 | 昭和電工株式会社 | 窒化物系半導体発光素子及びその製造方法 |

| JP4908837B2 (ja) * | 2005-12-13 | 2012-04-04 | キヤノン株式会社 | 発光素子アレイ及び画像形成装置 |

-

2006

- 2006-08-11 JP JP2006219791A patent/JP4960665B2/ja not_active Expired - Fee Related

-

2007

- 2007-08-03 EP EP07015267A patent/EP1887627A3/en not_active Withdrawn

- 2007-08-09 KR KR1020070079934A patent/KR100954051B1/ko not_active IP Right Cessation

- 2007-08-10 CN CNA2007101408925A patent/CN101123264A/zh active Pending

-

2008

- 2008-10-28 US US12/259,420 patent/US7786495B2/en not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105900239A (zh) * | 2013-09-30 | 2016-08-24 | 艾利迪公司 | 包括发光二极管的光电子装置 |

| CN105900239B (zh) * | 2013-09-30 | 2018-04-27 | 艾利迪公司 | 包括发光二极管的光电子装置 |

| WO2022094967A1 (zh) * | 2020-11-06 | 2022-05-12 | 京东方科技集团股份有限公司 | 发光二极管芯片及其制备方法、显示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1887627A2 (en) | 2008-02-13 |

| JP2008047618A (ja) | 2008-02-28 |

| JP4960665B2 (ja) | 2012-06-27 |

| KR20080014647A (ko) | 2008-02-14 |

| EP1887627A3 (en) | 2010-03-10 |

| KR100954051B1 (ko) | 2010-04-20 |

| US20090057693A1 (en) | 2009-03-05 |

| US7786495B2 (en) | 2010-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101123264A (zh) | 发光元件阵列和成像装置 | |

| US7491976B2 (en) | Light-emitting element array and image forming apparatus | |

| US8415680B2 (en) | Semiconductor composite apparatus, print head, and image forming apparatus | |

| US8816384B2 (en) | Semiconductor apparatus with thin semiconductor film | |

| US7871834B2 (en) | Combined semiconductor apparatus with thin semiconductor films | |

| US7122834B2 (en) | Semiconductor apparatus having adhesion layer and semiconductor thin film | |

| US8664668B2 (en) | Combined semiconductor apparatus with semiconductor thin film | |

| JP4908837B2 (ja) | 発光素子アレイ及び画像形成装置 | |

| US20070023767A1 (en) | Semiconductor apparatus having conductive layers and semiconductor thin films | |

| JP2007096160A (ja) | 半導体複合装置、及びこれらを用いたプリントヘッド並びに画像形成装置。 | |

| JP2007081081A (ja) | 3端子スイッチアレイ、3端子スイッチアレイ装置、半導体複合装置、および画像形成装置 | |

| US6781246B2 (en) | Semiconductor array device with single interconnection layer | |

| US7259397B2 (en) | Self-scanning light-emitting element array chip |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C12 | Rejection of a patent application after its publication | ||

| RJ01 | Rejection of invention patent application after publication |

Open date: 20080213 |